Rapid Prototyping of Digital Systems

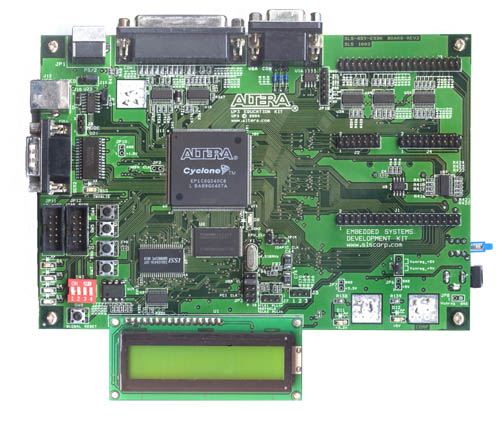

Rapid Prototyping of Digital Systems Quartus II Edition includes

four tutorials on the Altera Quartus II and NIOS II tool environment, an

overview of programmable logic, and IP cores with several easy-to-use input

and output functions. These features were developed to help students get

started quickly. Early design examples use schematic capture and IP cores

developed for the Altera UP FPGA boards. VHDL is used for more complex

designs after a short introduction to VHDL-based synthesis. New to this

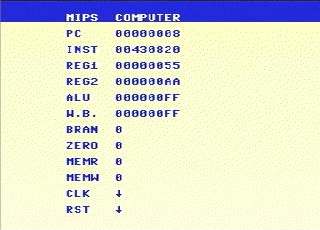

edition is an overview of System-on-a-Programmable Chip (SOPC) technology

and SOPC design examples for the UP3 using Altera's new NIOS II Processor

hardware and C software development tools. A full set of Altera's FPGA

CAD tools is included on the book's CD-ROM.

Hot Links

Book Errata and Software Update Page (includes new DE2 board projects)

Altera

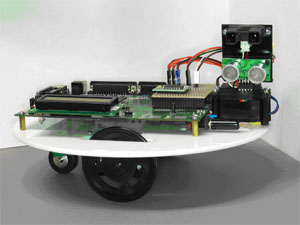

Some Design Examples (with photos and video clips)

Instructor Slides (all figures and tables from book)

Other Useful Reference Texts

Check Bookstores

Search Book's Website

The web site for the third edition is under development.

If you have comments or suggestions, email me at hamblen@ece.gatech.edu

This web page is not associated with or sponsored by Altera

Corporation. Altera is a trademark and service mark of Altera Corporation

in the United States and other countries. Altera products are the

intellectual property of Altera Corporation and are protected by copyright

laws and one or more U.S. and foreign patents and patent applications.