# Quartus II Handbook, Volume 1 Design & Synthesis

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com

qii5v1-2.1

Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

changes to any products and services at any time without nonce. After assumes to responsibility or hability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# Contents

| Chapter Revision Dates | <br>xi |

|------------------------|--------|

| Chapter Revision Dates | <br>X  |

| About this Handbook     | XIII |

|-------------------------|------|

| How to Contact Altera   | xiii |

| Typographic Conventions |      |

# **Section I. Design Flows**

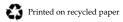

#### Chapter 1. Hierarchical Block-Based & Team-Based Design Flows

| Introduction                                                                           | . 1–1 |

|----------------------------------------------------------------------------------------|-------|

| Design Flows: Flattened versus Hierarchical Block-Based                                | 1–1   |

| Block-Based & Team-Based Designs                                                       | . 1–2 |

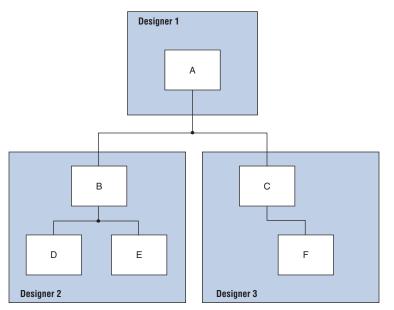

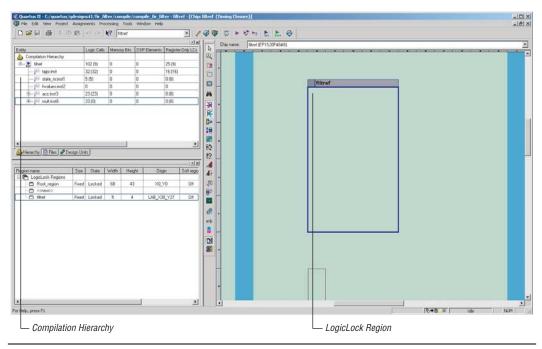

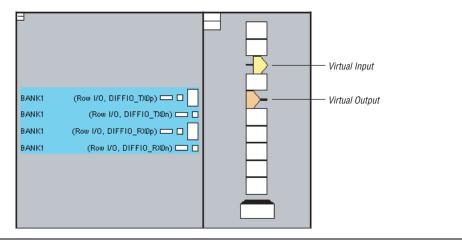

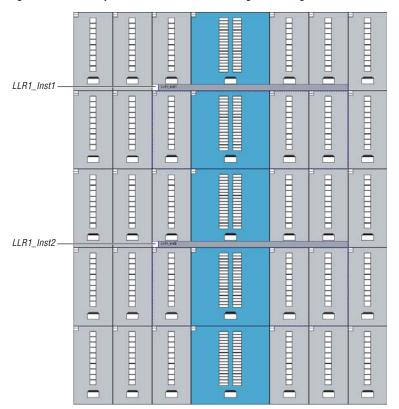

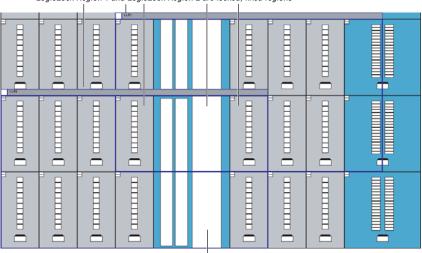

| Block-Based Design with the Quartus II LogicLock Methodology                           | 1–4   |

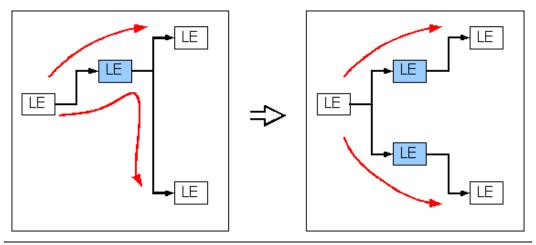

| Preserving Timing Results Using the LogicLock Flow                                     | 1–5   |

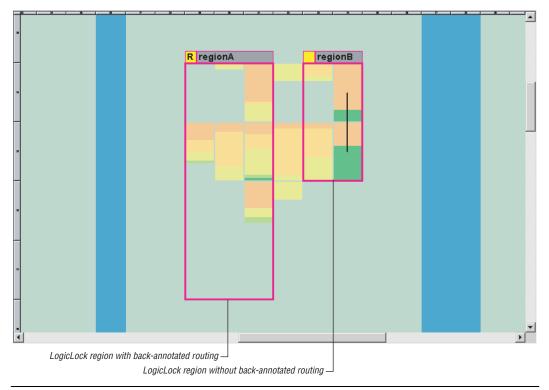

| Preserving Routing                                                                     | . 1–6 |

| Design Partitioning & Creating Multiple Netlist Files                                  | . 1–6 |

| Performing Incremental Fitting                                                         | 1–8   |

| Save a Node-Level Netlist into a Persistent Source File (Verilog Quartus Mapping File) | . 1–8 |

| Prevent Further Netlist Optimization                                                   | . 1–9 |

| Conclusion                                                                             | . 1–9 |

|                                                                                        |       |

#### Chapter 2. Quartus II Design Flow for MAX+PLUS II Users

| Introduction                                       |  |

|----------------------------------------------------|--|

| Chapter Overview                                   |  |

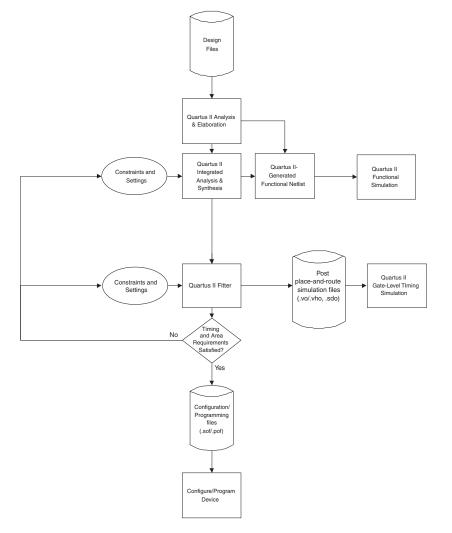

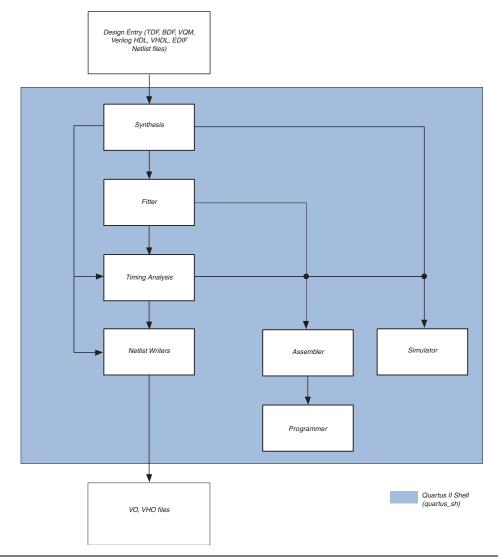

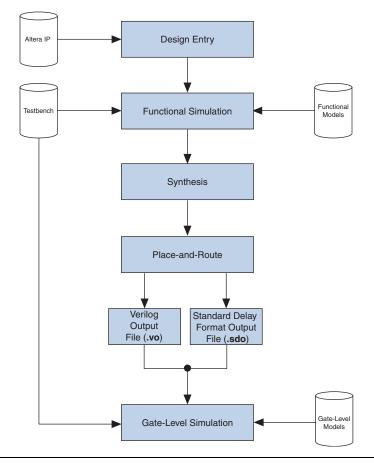

| Typical Design Flow                                |  |

| Device Support                                     |  |

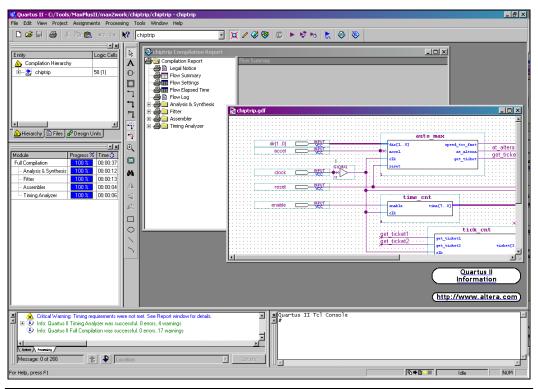

| Quartus II GUI Overview                            |  |

| Project Navigator                                  |  |

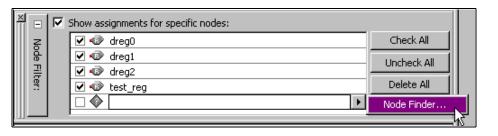

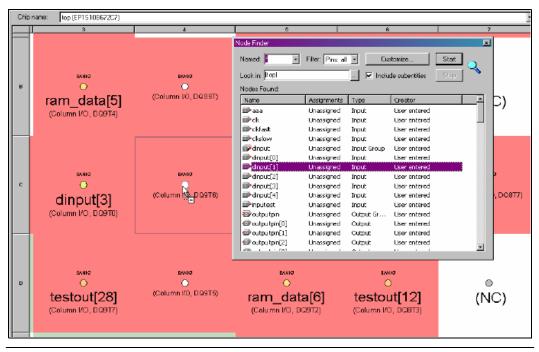

| Node Finder                                        |  |

| Tcl Console                                        |  |

| Messages                                           |  |

| Status                                             |  |

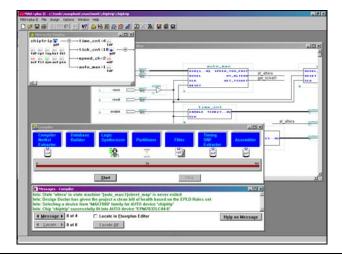

| Setting up MAX+PLUS II Look and Feel in Quartus II |  |

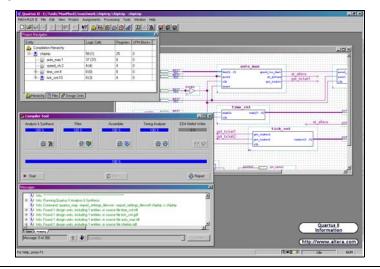

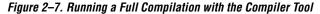

| Compiler Tool                                      |  |

| Converting an Existing MAX+PLUS II Design          |  |

| Converting MAX+PLUS II Graphic Design Files        |  |

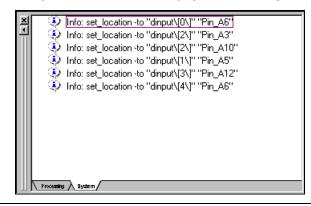

| Importing MAX+PLUS II Assignments                  |  |

| 1 0 0                                              |  |

| Quartus II Design Flow   | 2–13 |

|--------------------------|------|

| Creating a New Project   | 2–14 |

| Design Entry             |      |

| Making Assignments       |      |

| Synthesis                | 2–20 |

| Functional Simulation    |      |

| Place & Route            | 2–22 |

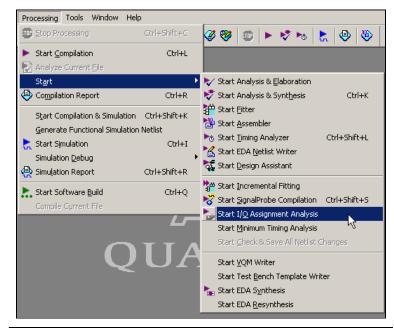

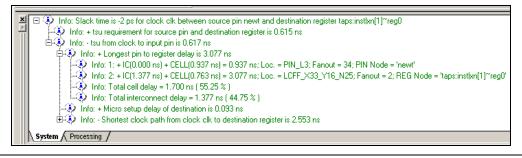

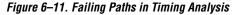

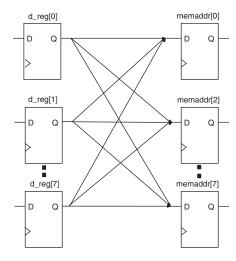

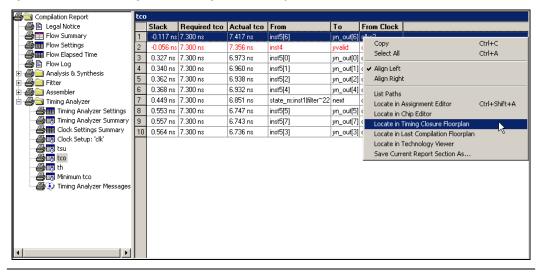

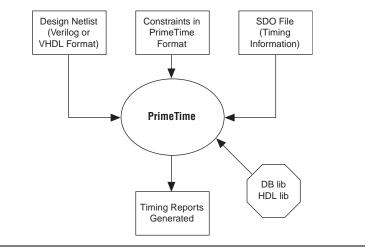

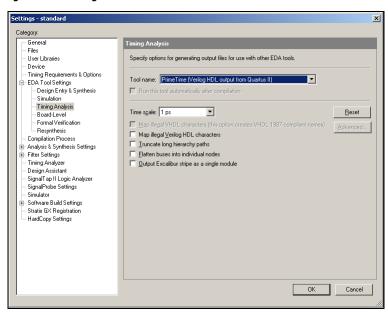

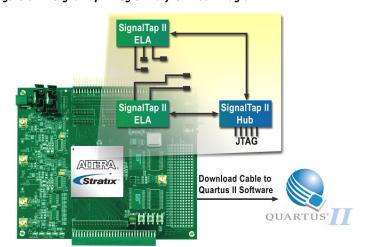

| Timing Analysis          | 2–23 |

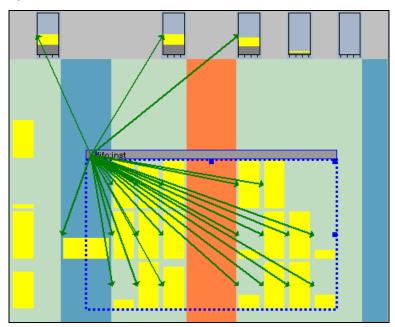

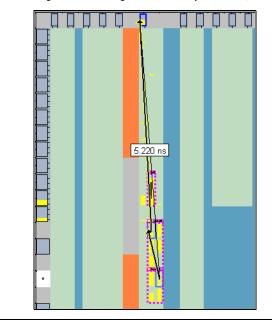

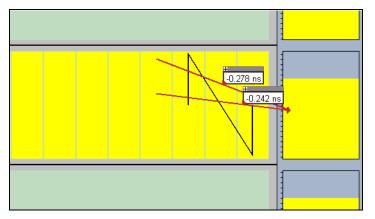

| Timing Closure Floorplan | 2–25 |

| Timing Simulation        | 2–26 |

| Power Estimation         |      |

| Programming              | 2–29 |

| Conclusion               |      |

| Quick Menu Reference     | 2–30 |

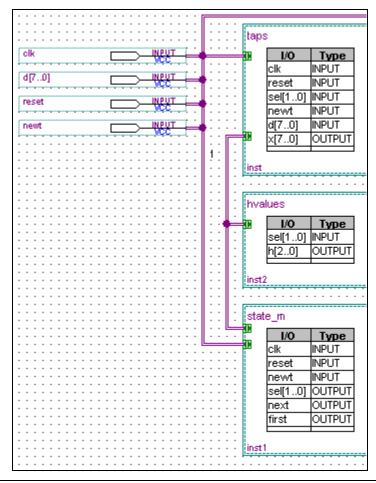

## Chapter 3. System Design Using SOPC Builder

| Introduction                   | 3–1 |

|--------------------------------|-----|

| SOPC Builder Peripherals       | 3–2 |

| Embedded Software Applications | 3–4 |

| Avalon Switch Fabric           |     |

| System Generation              | 3–6 |

| Simulation Model & Testbench   |     |

| Using SOPC Builder             | 3–6 |

| System Contents Page           |     |

| System Generation Page         | 3–9 |

| System Dependency Pages        |     |

| Generating a System            |     |

| Further Information            |     |

|                                |     |

#### Chapter 4. Quartus II Support for HardCopy Devices

| Introduction                                                           | 4–1  |

|------------------------------------------------------------------------|------|

| Features                                                               | 4–2  |

| HARDCOPY_FPGA_PROTOTYPE, HardCopy Stratix, and Stratix Devices         | 4–3  |

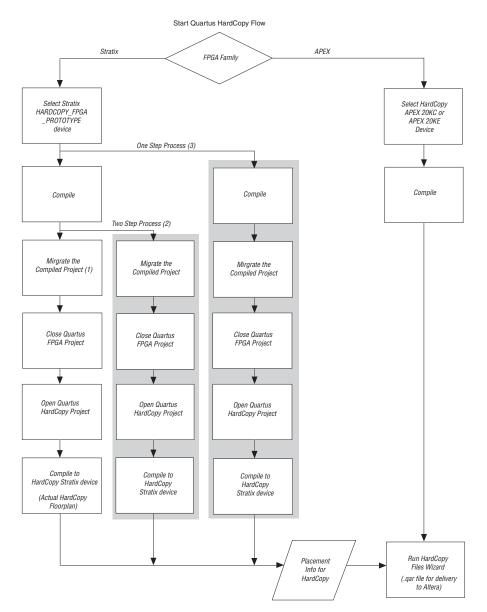

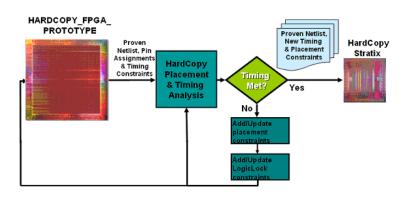

| HardCopy Design Flow                                                   | 4–4  |

| The Design Flow Steps of the One Step Process                          | 4–6  |

| How to Design HardCopy Devices                                         | 4–6  |

| Targeting Designs to HARDCOPY_FPGA_PROTOTYPE Devices                   | 4–6  |

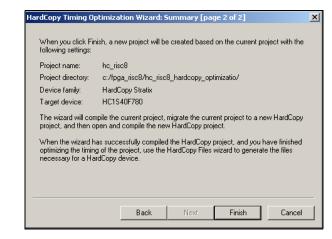

| Tcl Support for HardCopy Migration                                     | 4–9  |

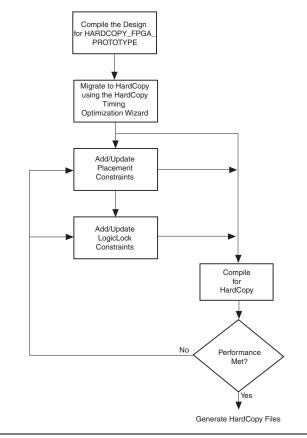

| Design Optimization & Performance Estimation                           | 4–10 |

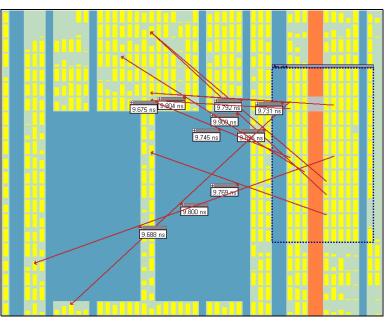

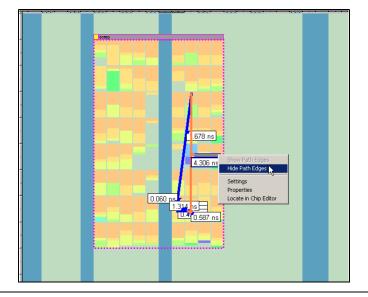

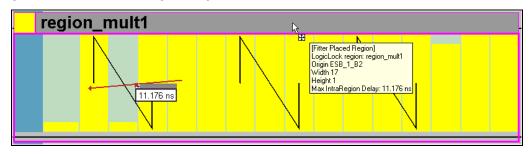

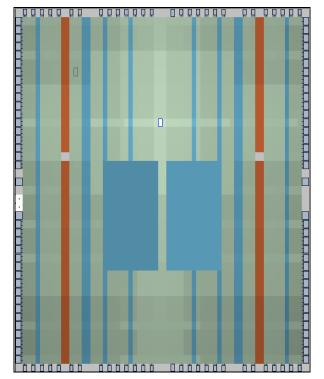

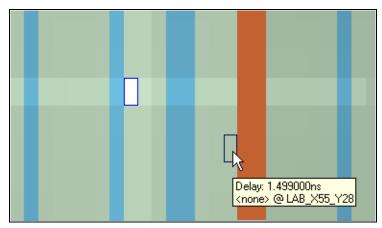

| HardCopy Floorplans & Timing Models                                    |      |

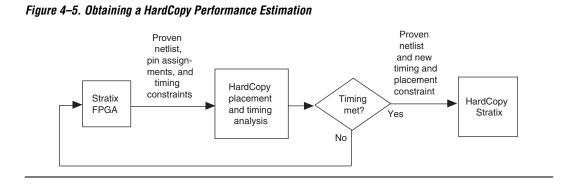

| Performance Estimation                                                 | 4–10 |

| Placement Constraints                                                  | 4–12 |

| Location Constraints                                                   |      |

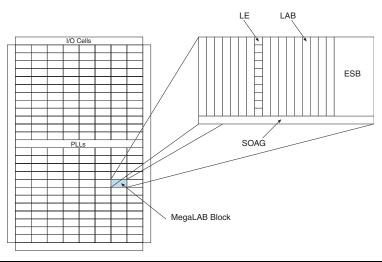

| LAB Assignments                                                        | 4–13 |

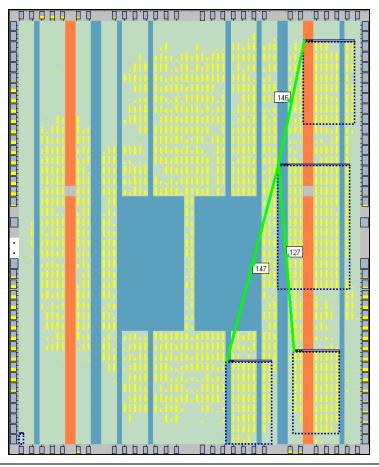

| LogicLock Assignments                                                  |      |

| Targeting Designs to HardCopy APEX 20KC and HardCopy APEX 20KE Devices | 4–14 |

| Checking Designs for HardCopy Design Guidelines                        | 4–15 |

| Design Assistant Settings                 | 4–15 |

|-------------------------------------------|------|

| Running Design Assistant                  | 4–15 |

| Reports and Summary                       |      |

| Generating the HardCopy Design Database   |      |

| Static Timing Analysis (STA)              |      |

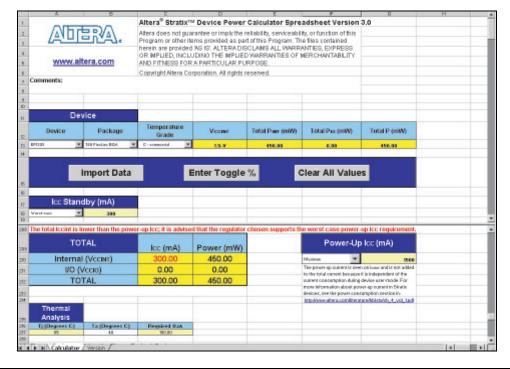

| Power Estimation                          | 4–17 |

| HardCopy Stratix Power Calculator         | 4–17 |

| Opening HardCopy Stratix Power Calculator | 4–18 |

| HardCopy APEX 20K Power Calculator        |      |

| Power Calculators for FPGAs               |      |

| Tcl Support for HardCopy Stratix          | 4–20 |

| Conclusion                                |      |

| Related Documents                         | 4–21 |

#### **Chapter 5. Engineering Change Management**

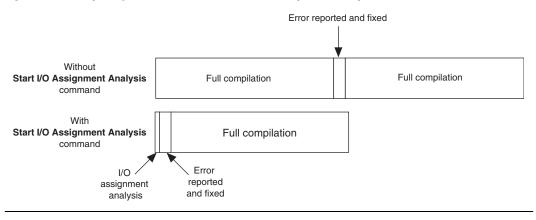

| Impact of Last Minute Design Changes | 5–1 |

|--------------------------------------|-----|

| Performance                          | 5–1 |

| Compile Time                         | 5–2 |

| Verification                         | 5–2 |

| Documentation                        | 5–2 |

| ECO Support                          | 5–2 |

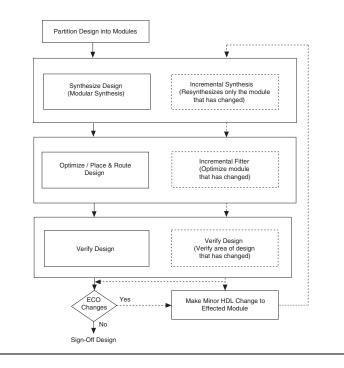

| ECO Support at the HDL Level         | 5–3 |

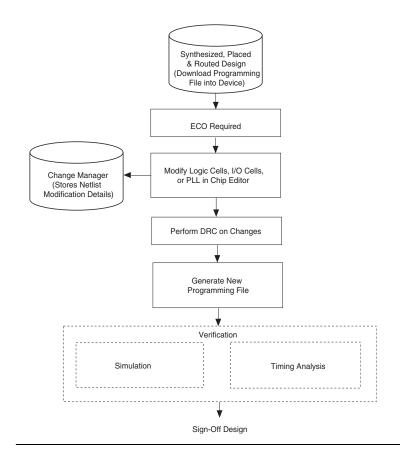

| ECO Support at the Netlist Level     | 5–5 |

| Conclusion                           |     |

|                                      |     |

# Section II. Design Guidelines

| Revision History Se | ection 1 | II– | -1 |

|---------------------|----------|-----|----|

|---------------------|----------|-----|----|

#### **Chapter 6. Design Recommendations for Altera Devices**

| Introduction                                              |  |

|-----------------------------------------------------------|--|

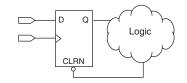

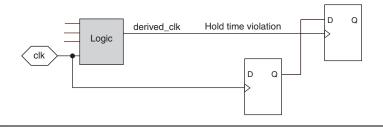

| Synchronous FPGA Design Practices                         |  |

| Fundamentals of Synchronous Design                        |  |

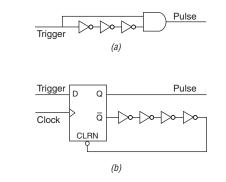

| Hazards of Asynchronous Design                            |  |

| Recommended Design Techniques                             |  |

| Combinational Logic Structures                            |  |

| Clocking Schemes                                          |  |

| Hierarchical Design Partitioning                          |  |

| Targeting Clock & Register-Control Architectural Features |  |

| Conclusion                                                |  |

|                                                           |  |

#### **Chapter 7. Recommended HDL Coding Styles**

| Introduction                                     | 7–1 |

|--------------------------------------------------|-----|

| Instantiating and Inferring Altera Megafunctions | 7–1 |

| Instantiating Altera Megafunctions in HDL Code   |     |

| Inferring Megafunctions from HDL Code            |     |

| Counters                                             |                   |

|------------------------------------------------------|-------------------|

| Adder/Subtractors                                    |                   |

| Multipliers                                          |                   |

| Multiply-Accumulators & Multiply-Adders              |                   |

| RAM                                                  |                   |

| ROM                                                  |                   |

| Shift Registers                                      |                   |

| Device-Specific Coding Recommenda-tions              |                   |

| Secondary Control Signals in Registers or Flip-Flops |                   |

| Tri-State Signals                                    |                   |

| Adder Trees                                          |                   |

| General Coding Recommenda-tions                      |                   |

| Latches                                              |                   |

| State Machines                                       |                   |

|                                                      | Multiplexers 7–38 |

| Conclusion                                           |                   |

# Section III. Synthesis

| <b>Revision History</b> |  |

|-------------------------|--|

|-------------------------|--|

#### Chapter 8. Quartus II Integrated Synthesis

| Introduction                                              |      |

|-----------------------------------------------------------|------|

| Verilog HDL & VHDL Support                                | 8–1  |

| Verilog HDL                                               | 8–1  |

| VHDL                                                      | 8–2  |

| Types of Synthesis Options                                | 8–3  |

| Synthesis Directives                                      |      |

| Synthesis Attributes                                      | 8–5  |

| Quartus II Logic Options                                  | 8–6  |

| Quartus II Synthesis Options                              |      |

| Translate Off & On                                        | 8–7  |

| Read Comments as HDL                                      | 8–7  |

| Full Case                                                 |      |

| Parallel Case                                             |      |

| Keep Combinational Node/Implement as Output of Logic Cell |      |

| Preserve Registers                                        |      |

| Maximum Fan-Out                                           |      |

| Optimization Technique                                    |      |

| State Machine Processing                                  |      |

| Preserve Hierarchical Boundary                            |      |

| Restructure Multiplexers                                  |      |

| Power-Up Level                                            |      |

| Power-Up Don't Care                                       |      |

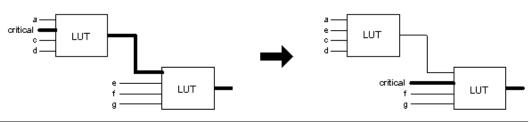

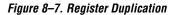

| Remove Duplicate Logic                                    |      |

| Remove Duplicate Registers                                |      |

| Remove Redundant Logic Cells                              | 8–20 |

| Megafunction Inference Control                           | 8–20 |

|----------------------------------------------------------|------|

| RAM Style                                                | 8–22 |

| Setting Other Quartus II Options in Your HDL Source Code | 8–23 |

| Use I/O Flip-Flops                                       |      |

| Altera Attribute                                         |      |

| Chip Pin                                                 | 8–27 |

| Scripting Support                                        | 8–29 |

| Quartus II Synthesis Options                             |      |

| Assigning a Pin                                          |      |

| Conclusion                                               |      |

|                                                          |      |

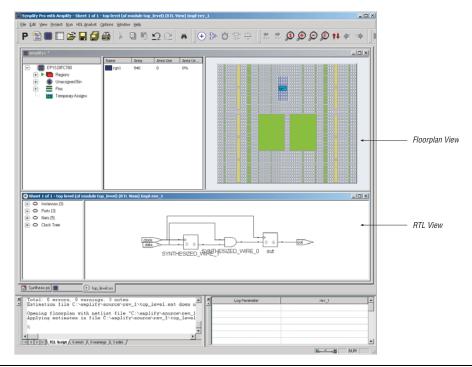

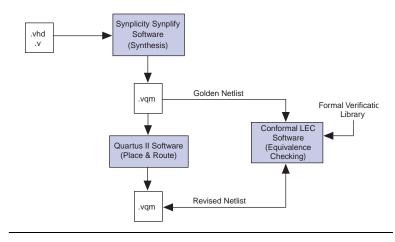

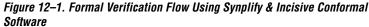

## Chapter 9. Synplicity Synplify & SynplifyPro Support

| Introduction                                                                        |           |

|-------------------------------------------------------------------------------------|-----------|

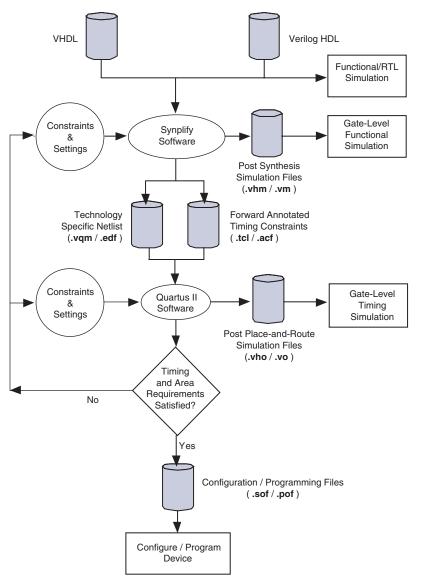

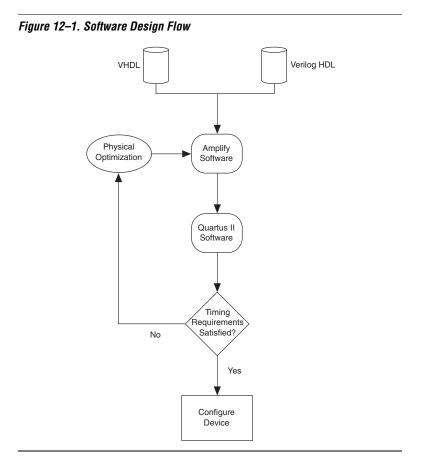

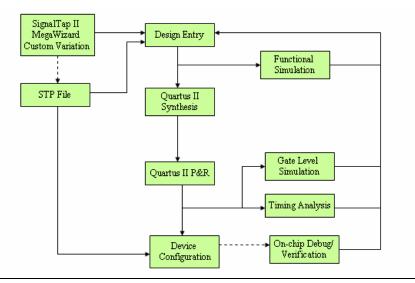

| Design Flow                                                                         | 9–1       |

| Synplify Optimization Strategies                                                    |           |

| Implementations in Synplify Pro                                                     |           |

| Timing-driven Synthesis Settings                                                    |           |

| Finite State Machine (FSM) Compiler                                                 |           |

| General Optimization Attributes & Options                                           | 9–10      |

| Altera Specific Attributes                                                          | 9–11      |

| Exporting Designs to the Quartus II Software Using NativeLink Integration           | 9–13      |

| Running the Quartus II Software from within the Synplify Software                   | 9–14      |

| Using the Quartus II Software to Launch the Synplify Software                       |           |

| Cross-Probing with the Quartus II Software                                          | 9–15      |

| Enabling Cross-Probing                                                              | 9–15      |

| Cross-Probing from the Quartus II Software                                          | 9–16      |

| Cross-Probing from the Synplify Software                                            | 9–16      |

| Guidelines for Altera Megafunctions & Architecture-Specific Features                |           |

| Instantiating Altera Megafunctions Using the MegaWizard Plug-In Manager             | 9–18      |

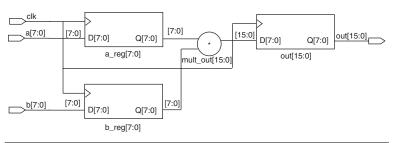

| Inferring Altera Megafunctions from HDL Code                                        |           |

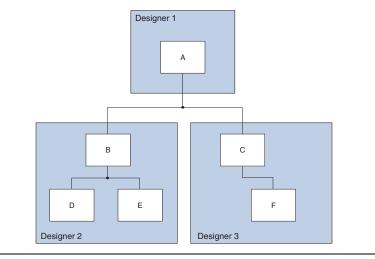

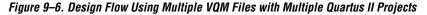

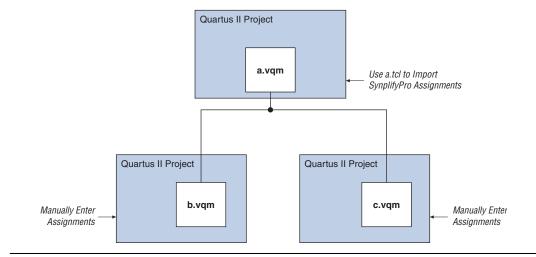

| Hierarchy & Design Considerations with Multiple VQM Files                           |           |

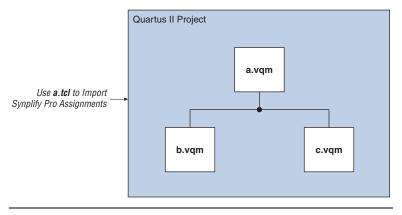

| Creating a Design with Multiple VQM Files                                           | 9–29      |

| Creating a Design with Multiple VQM Files using Multipoint Synthesis (Synplify 9–30 | Pro only) |

| Generating a Design with Multiple VQM Files Using Black Boxes                       |           |

| Conclusion                                                                          | 9–41      |

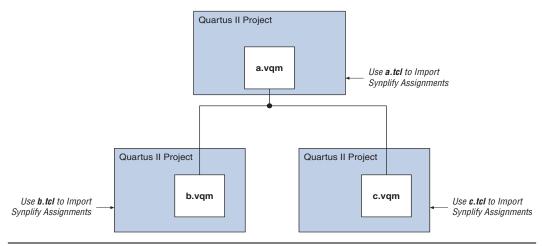

# Chapter 10. Mentor Graphics LeonardoSpectrum Support

| Introduction                                        | 10-1 |

|-----------------------------------------------------|------|

| Design Flow                                         | 10–1 |

| Optimization Strategies                             |      |

| Timing-Driven Synthesis                             |      |

| Other Constraints                                   |      |

| Timing Analysis with the Leonardo-Spectrum Software | 10–7 |

| Exporting Designs Using NativeLink Integration      | 10-8 |

| Generating Netlist Files                            |      |

| Including Design Files for Black-Boxed Modules               | 10–8  |

|--------------------------------------------------------------|-------|

| Passing Constraints Via Scripts                              | 10–8  |

| Integration with the Quartus II Software                     | 10–9  |

| Guidelines for Altera Megafunctions & LPM Functions          | 10–9  |

| Inferring Multipliers & DSP Functions                        | 10–11 |

| Controlling DSP Block Inference                              | 10–12 |

| Block-based Design with the Quartus II LogicLock Methodology | 10–18 |

| Hierarchy & Design Considerations                            | 10–19 |

| Creating a Design with Multiple EDIF Files                   | 10–20 |

| Generating Multiple EDIF Files Using Black Boxes             | 10–24 |

| Incremental Synthesis Flow                                   | 10–29 |

| Conclusion                                                   | 10–31 |

#### Chapter 11. Mentor Graphics Precision RTL Synthesis Support

| The second |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Introduction 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

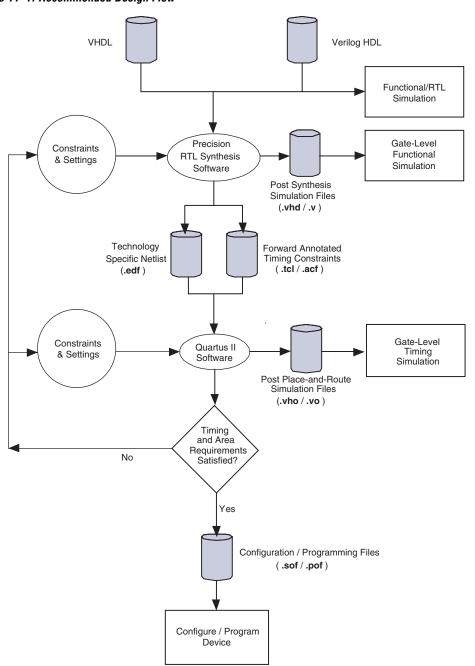

| Design Flow 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11–1 |

| Creating a Project & Compiling a Design 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11–5 |

| Creating a Project 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11–5 |

| Compiling the Design 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11–6 |

| Setting Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11–6 |

| Setting Timing Constraints 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11–7 |

| Setting Mapping Constraints 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11–7 |

| Assigning Pin Numbers & I/O Settings 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11–8 |

| Assigning I/O Registers 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11–9 |

| Disabling I/O Pad Insertion 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11–9 |

| Controlling Fan-Out on Data Nets 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1–10 |

| Synthesizing the Design & Evaluating the Results 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1–11 |

| Obtaining Accurate Logic Utilization & Timing Analysis Reports 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1–11 |

| Megafunctions & Architecture-Specific Features 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1–14 |

| Instantiating Altera Megafunctions Using the MegaWizard Plug-In Manager 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1–15 |

| Inferring Altera Megafunctions from HDL Code 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1–17 |

| Block-Based Design with the Quartus II LogicLock Methodology 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1–23 |

| Hierarchy & Design Considerations 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1–23 |

| Creating a Design with Separate Blocks for the LogicLock Methodology 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1–24 |

| Creating a Design with Separate Blocks Using the LogicLock Attribute in a Single Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n    |

| Project 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Generating a Design with Multiple EDIF Files Using Black Boxes 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1–26 |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1–30 |

# Chapter 12. Synopsys FPGA Compiler II BLIS & Quartus II LogicLock Design Flow

| Introduction                                          | 12 - 1 |

|-------------------------------------------------------|--------|

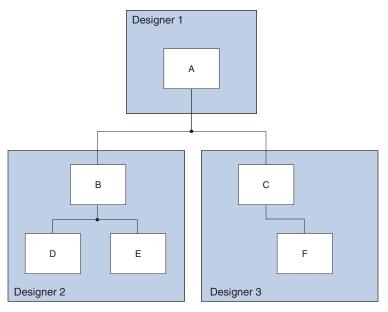

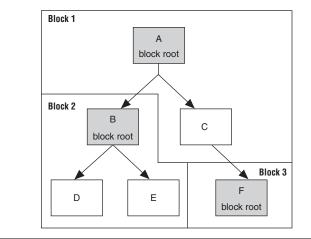

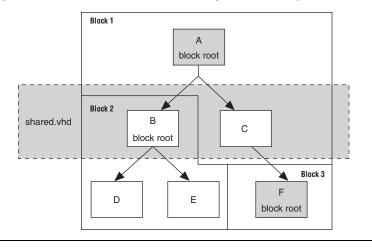

| Design Hierarchy                                      | 12–1   |

| Block-Level Incremental Synthesis                     |        |

| FPGA Compiler II Design Block                         |        |

| FPGA Compiler II & Quartus II Synthesis               | 12–3   |

| Block Root                                            |        |

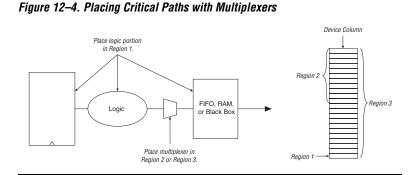

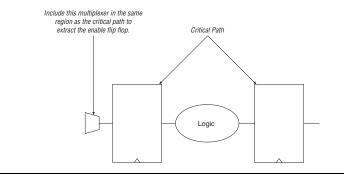

| How the BLIS Feature Works with the LogicLock Feature | 12–4   |

| Hierarchy Considerations                                    | 12–5 |

|-------------------------------------------------------------|------|

| Time Stamp Synthesis                                        | 12–6 |

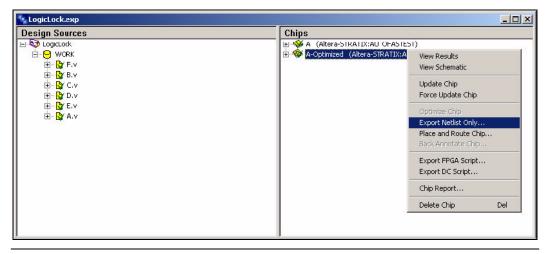

| Creating & Maintaining a Design                             |      |

| Opening the Modules Constraint Table & Labeling Block Roots |      |

| Exporting Block-Level Netlist Files                         |      |

| Changing Source Within a Block                              |      |

| Removing a Block Root                                       |      |

| Using BLIS Shell Commands                                   |      |

| Conclusion                                                  |      |

#### Chapter 13. Synopsys Design Compiler FPGA Support

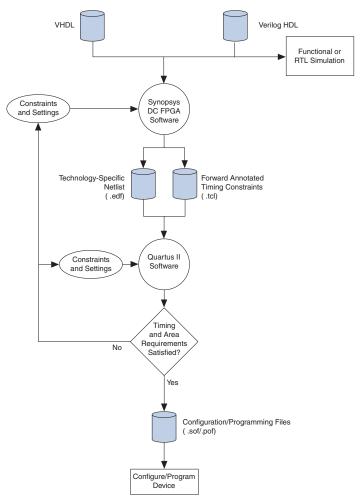

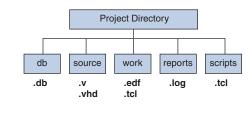

| Design Flow Using the DC FPGA Software & the Quartus II Software              | 13–2  |

|-------------------------------------------------------------------------------|-------|

| Setup of the DC FPGA Software Environment for Altera Device Families          | 13–3  |

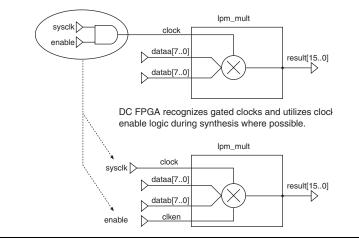

| Megafunctions & Architecture-Specific Features                                | 13–5  |

| Reading MegaWizard-Generated Variation Wrapper Files                          | 13–7  |

| Using MegaWizard-Generated Variation Wrapper Files in a Black-Box Methodology | 13–7  |

| Inferring Altera Megafunctions from HDL Code                                  | 13–8  |

| Reading Design Files into the DC FPGA Software                                | 13–9  |

| Selecting a Target Device                                                     | 13–11 |

| Compilation & Synthesis                                                       | 13–14 |

| Saving Synthesis Results                                                      | 13–17 |

| Exporting Designs to the Quartus II Software                                  | 13–18 |

| Place & Route with the Quartus II Software                                    | 13–21 |

| Conclusion                                                                    | 13–21 |

|                                                                               |       |

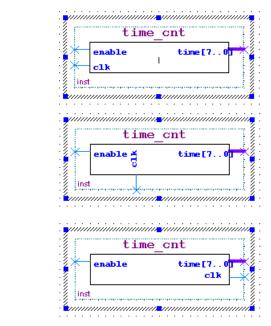

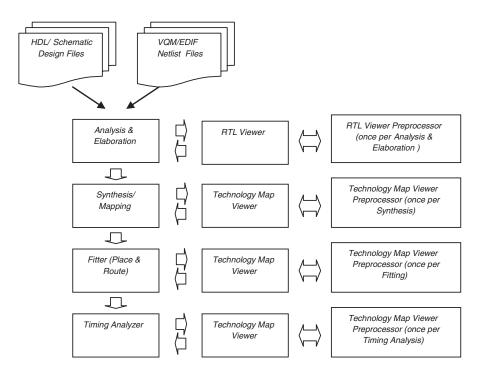

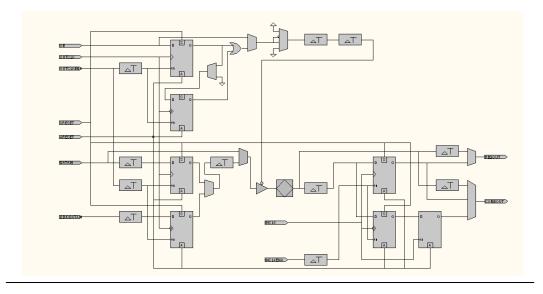

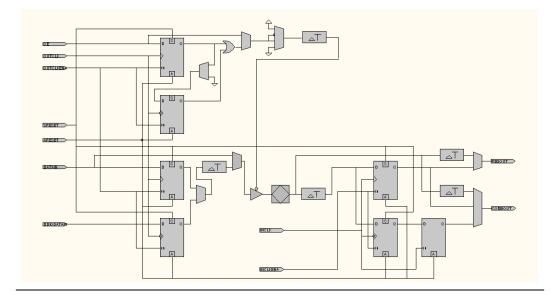

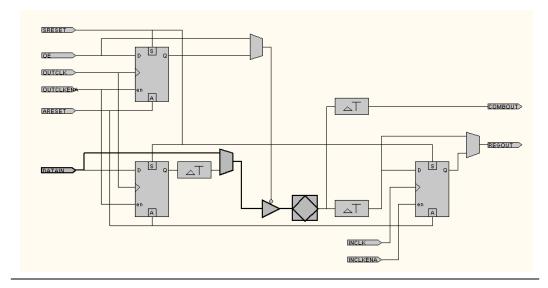

# Chapter 14. Analyzing Designs with the Quartus II RTL Viewer & Technology Map Viewer

| Introduction                                                 | 14–1  |

|--------------------------------------------------------------|-------|

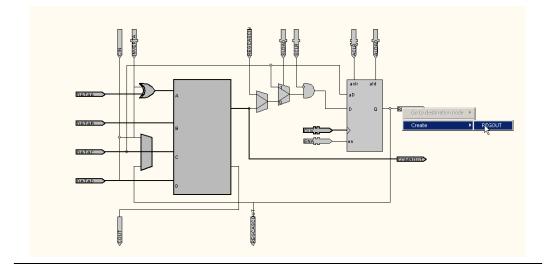

| RTL Viewer Overview                                          | 14–1  |

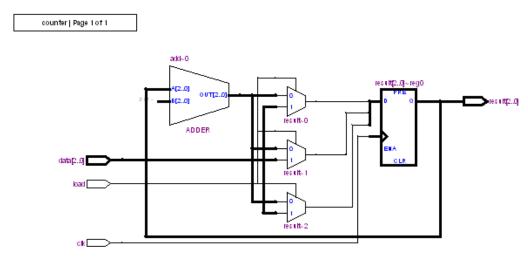

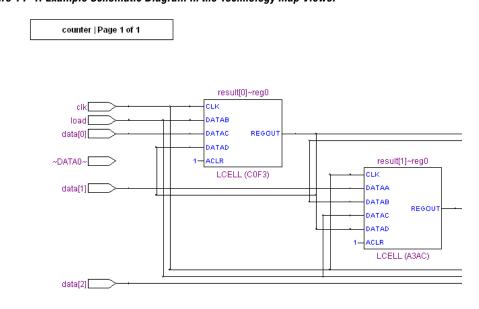

| Technology Map Viewer Overview                               | 14–2  |

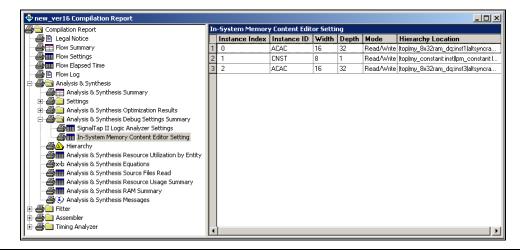

| Quartus II Design Flow with the RTL & Technology Map Viewers | 14–3  |

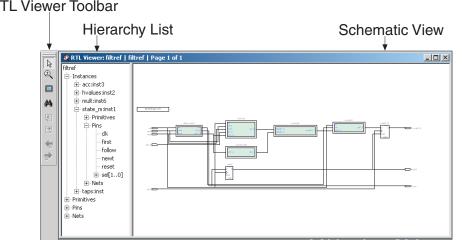

| Introduction to the User Interface                           | 14–4  |

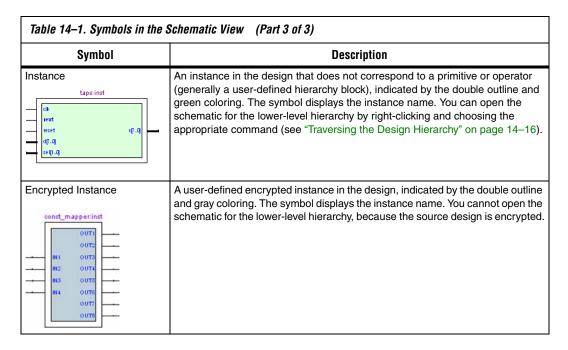

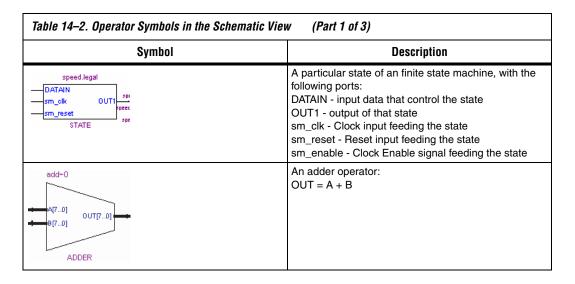

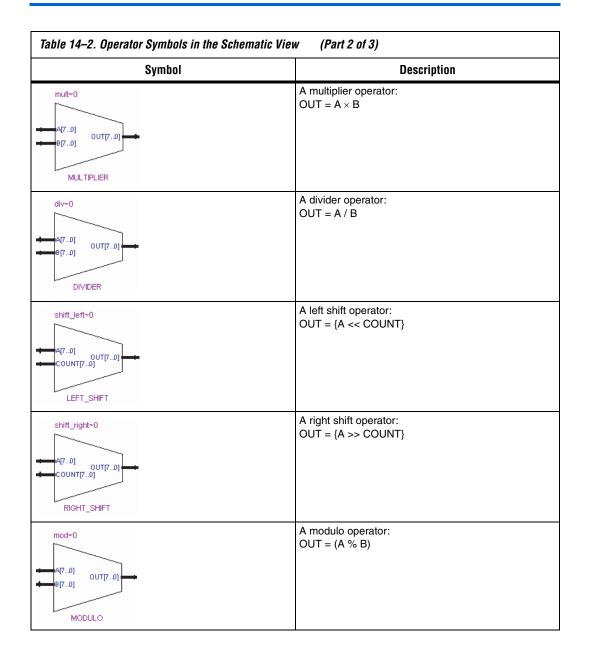

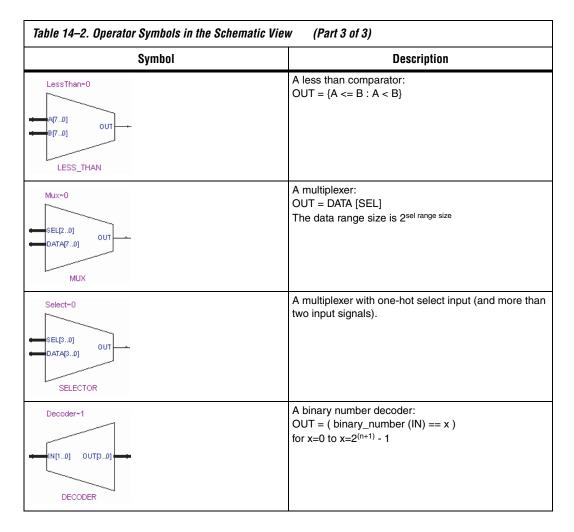

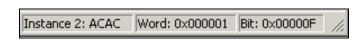

| Schematic View                                               | 14–5  |

| Hierarchy List                                               | 14–12 |

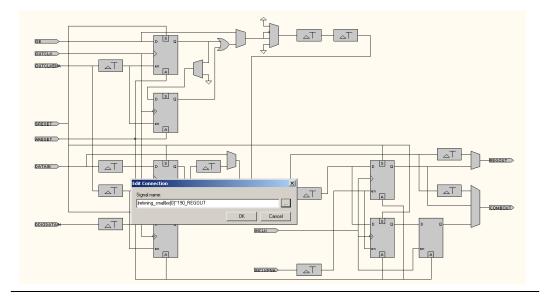

| Navigating the Schematic View                                | 14–13 |

| Zooming & Magnification                                      | 14–13 |

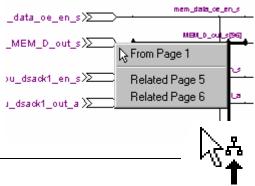

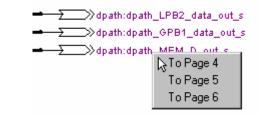

| Page Partitioning in the Schematic View                      | 14–14 |

| Traversing the Design Hierarchy                              | 14–16 |

| Back & Forward Page Viewing                                  | 14–17 |

| Go to Net Driver                                             | 14–17 |

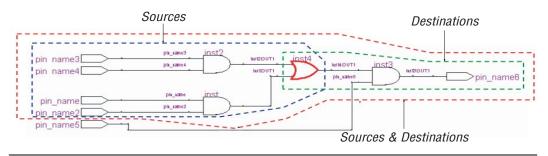

| Filtering in the Schematic View                              | 14–17 |

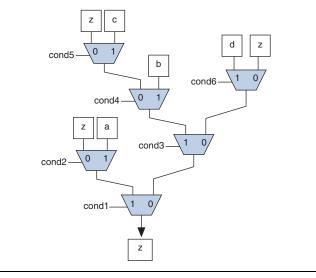

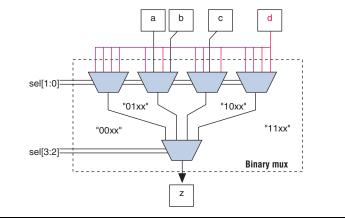

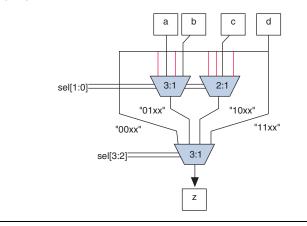

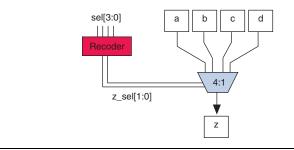

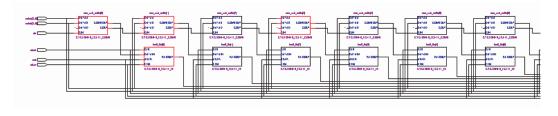

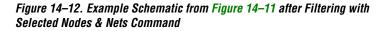

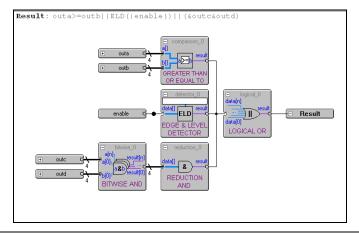

| Examples of Filtered Netlists                                | 14–19 |

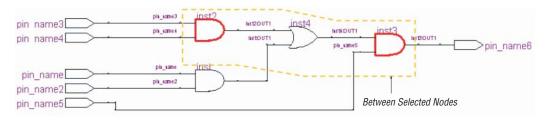

| Expanding a Filtered Netlist                                 | 14–21 |

| Reducing a Filtered Netlist                                  | 14–21 |

| Probing to Source Design File & Other Quartus II Features    | 14–22 |

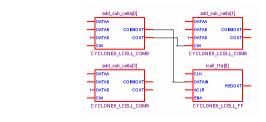

| Viewing a Timing Path in the Technology Map Viewer           | 14–22 |

| Other Features in the Schematic Viewer                       | 14–24 |

| Tooltips                                                     | 14–24 |

|                                                              |       |

| Displaying Net Names                                              |   |

|-------------------------------------------------------------------|---|

| Full Screen View                                                  |   |

| Find Command                                                      |   |

| Exporting Schematic as JPEG or BMP Image & Copying to Clipboard   |   |

| Printing                                                          |   |

| Using the RTL & Technology Map Viewers to Analyze Design Problems |   |

| Conclusion                                                        |   |

|                                                                   |   |

| Index                                                             | 1 |

# **Chapter Revision Dates**

The chapters in this book, *Quartus II Handbook, Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

| Chapter 1. | Revised:         | ck-Based & Team-Based Design Flows<br><i>August 2004</i><br>qii51001-2.1 |

|------------|------------------|--------------------------------------------------------------------------|

| Chapter 2. |                  | gn Flow for MAX+PLUS II Users                                            |

|            |                  | June 2004                                                                |

|            | Part number:     | qii51002-2.0                                                             |

| Chapter 3. | System Design U  | Using SOPC Builder                                                       |

|            |                  | June 2004                                                                |

|            | Part number:     | qii51003-2.0                                                             |

| Chapter 4. | Quartus II Supp  | ort for HardCopy Devices                                                 |

|            | Revised:         | June 2004                                                                |

|            | Part number:     | qii51004-2.0                                                             |

| Chapter 5. | Engineering Cha  | ange Management                                                          |

|            | Revised:         | June 2004                                                                |

|            | Part number:     | qii51005-2.0                                                             |

| Chapter 6. | Design Recomm    | endations for Altera Devices                                             |

|            | Revised:         | June 2004                                                                |

|            | Part number:     | qii51006-2.0                                                             |

| Chapter 7. | Recommended 1    | HDL Coding Styles                                                        |

| -          | Revised:         | June 2004                                                                |

|            | Part number:     | qii51007-2.0                                                             |

| Chapter 8. | Quartus II Integ | rated Synthesis                                                          |

|            | Revised:         | June 2004                                                                |

|            | Part number:     | qii51008-2.0                                                             |

| Chapter 9. | Synplicity Synpl | lify & SynplifyPro Support                                               |

|            | Revised:         | June 2004                                                                |

|            | Part number:     | qii51009-2.0                                                             |

- Chapter 10. Mentor Graphics LeonardoSpectrum Support Revised: June 2004 Part number: qii51010-2.0

- Chapter 11. Mentor Graphics Precision RTL Synthesis Support Revised: June 2004 Part number: qii51011-2.0

- Chapter 12. Synopsys FPGA Compiler II BLIS & Quartus II LogicLock Design Flow Revised: June 2004 Part number: qii51012-1.0

- Chapter 13. Synopsys Design Compiler FPGA Support Revised: June 2004 Part number: qii51014-1.0

- Chapter 14. Analyzing Designs with the Quartus II RTL Viewer & Technology Map Viewer Revised: June 2004 Part number: qii51013-2.0

# About this Handbook

This handbook provides comprehensive information about the Altera® Quartus®II design software, version 4.0..

# How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                         |

|--------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | altera.com/mysupport/                                       |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | (408) 544-7000 (1)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) |

| Product literature             | www.altera.com                                                 | www.altera.com                                              |

| Altera literature services     | lit_req@altera.com (1)                                         | lit_req@altera.com (1)                                      |

| Non-technical customer service | (800) 767-3753                                                 | (408) 544-7000<br>(7:30 a.m. to 5:30 p.m. Pacific Time)     |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                              |

Note to table:

(1) You can also contact your local Altera sales office or sales representative.

## Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                     |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                  |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                      |

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic type                         | Internal timing parameters and variables are shown in italic type. Examples: $t_{P A}$ , $n + 1$ .                                                                                                                                                                                                                      |

|                                     | Variable names are enclosed in angle brackets (< >) and shown in italic type.<br>Example: <i><file name=""></file></i> , <i><project name="">.pof</project></i> file.                                                                                                                                                   |

| Initial Capital Letters             | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |