ECE 3055 Computer Architecture and Operating Systems

J. Hamblen

Full die

photograph of the MIPS R2000 RISC Microprocessor.

The 1986 MIPS

R2000 with five pipeline stages and 450,000 transistors was the world’s first

commercial RISC microprocessor.

Photograph

©1995-2004 courtesy of Michael Davidson, Florida State University, http://micro.magnet.fsu.edu/chipshots.

Course materials (after class extra copies

left with lab TAs)

- Syllabus

- Slides

& Handouts(*.ppt, *.pdf), Old Tests(3055t*.*), Homeworks

(3055h*.doc), Quizzes (3055q*.*), and Labs(3055l*.doc) - last alpha character

indicates version, later letters are more recent

Software &

Related links

- ECE 3055 Lab

Page (GO TO THIS PAGE FOR IMPORTANT ANNOUNCEMENTS TA HOURS AND

ABOUT LAB GRADING!!)

- New MARS

MIPS Simulator - a JAVA-based alternative to SPIM with more features

- Old SPIM Simulator

- Crimson

Editor for SPIM

- Altera Quartus Web Edition

9.1 for Student PCs - Caution 10.0 and higher will require knowledge

of ModelSIM

- 32-bit MIPS

VHDL Model Instructions

- MIPS Wintim Files

- Visual C

tutorial

- Visual J

tutorial

- Microsoft Software

for ECE students

- Free C++ and

Java electronic textbooks

- Free

C++ and Java electronic textbooks (online GT only)

New 16 core

AMD Opteron 6200 processor

Figures &

Slides from Computer Organization & Design by Patterson and Hennessy 4th

Edition

Figures & Slides from Operating Systems Concepts by Silberschatz & Galvin 8th Edition

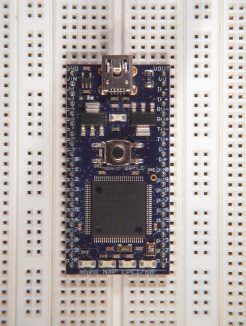

A Student VHDL-based timing simulation of the MIPS Processor

running in the Free Altera Quartus

II FPGA CAD tool.