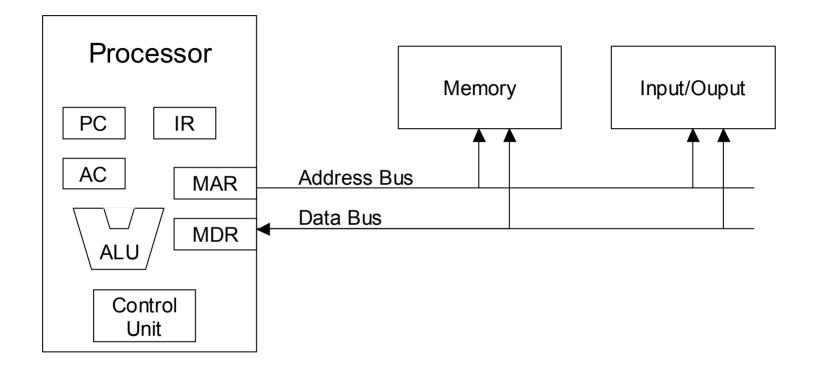

Figure 9.1 Architecture of a Simple Computer System.

|    | Opcode |   | Address | , |

|----|--------|---|---------|---|

| 15 |        | 8 | 7       | 0 |

**Figure 9.2** Simple µP 3 Computer Instruction Format.

| <b>Instruction Mnemonic</b> | <b>Operation Preformed</b>           | <b>Opcode Value</b> |

|-----------------------------|--------------------------------------|---------------------|

| ADD address                 | AC <= AC + contents of memory addres | <b>s</b> 00         |

| STORE address               | contents of memory address <= AC     | 01                  |

| LOAD address                | AC <= contents of memory address     | 02                  |

| JUMP address                | PC <= address                        | 03                  |

| JNEG address                | If AC < 0 Then PC <= address         | 04                  |

Figure 9.3 Basic µP 3 Computer Instructions.

| Assembly Language | <b>MachineLanguage</b> |  |  |  |

|-------------------|------------------------|--|--|--|

| LOAD B            | 0211                   |  |  |  |

| ADD C             | 0012                   |  |  |  |

| STORE A           | 0110                   |  |  |  |

**Figure 9.4** Example Computer Program for A = B + C.

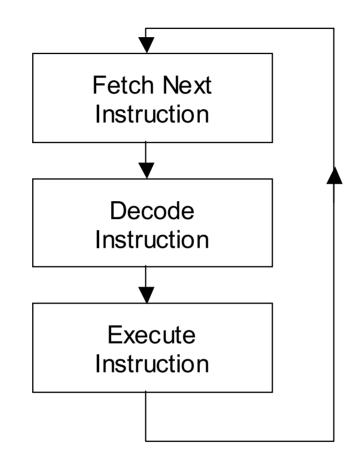

Figure 9.5 Processor Fetch, Decode and Execute Cycle.

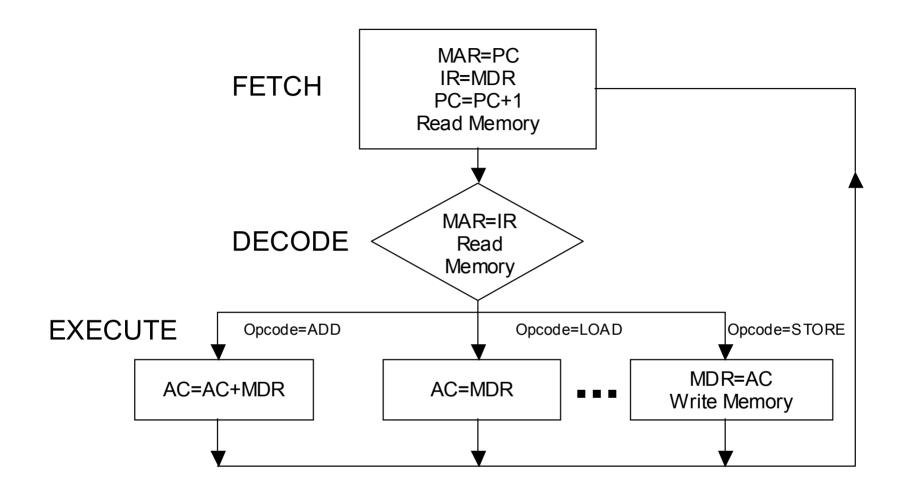

Figure 9.6 Detailed View of Fetch, Decode, and Execute for the µP 3 Computer Design.

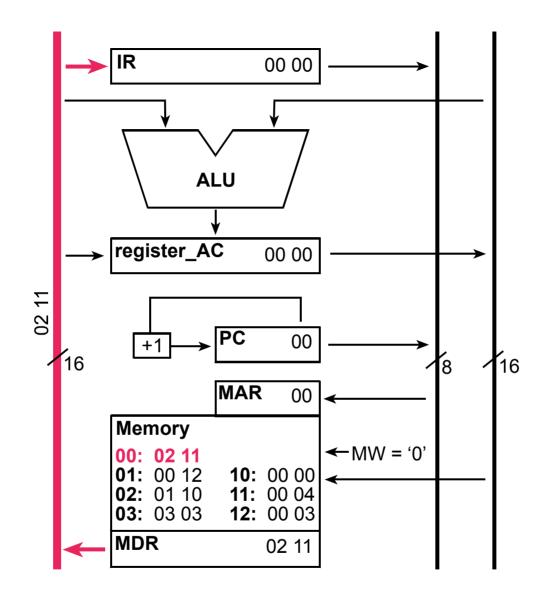

Figure 9.7 Datapath used for the µP 3 Computer Design. Values shown after applying reset.

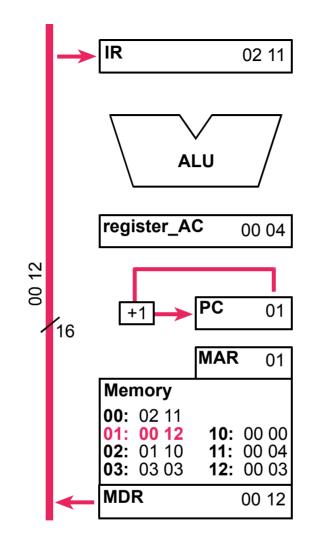

Figure 9.8 Register transfers in the ADD instruction's Fetch State.

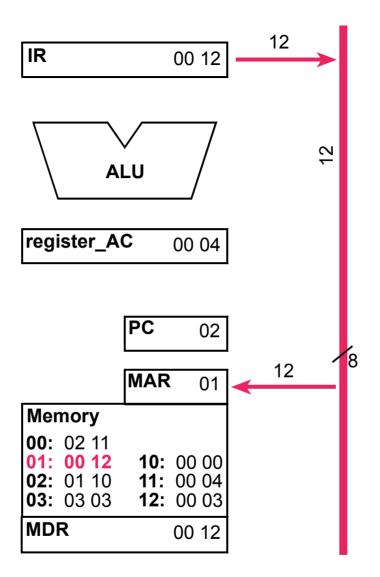

Figure 9.9 Register transfers in the ADD instruction's Decode State.

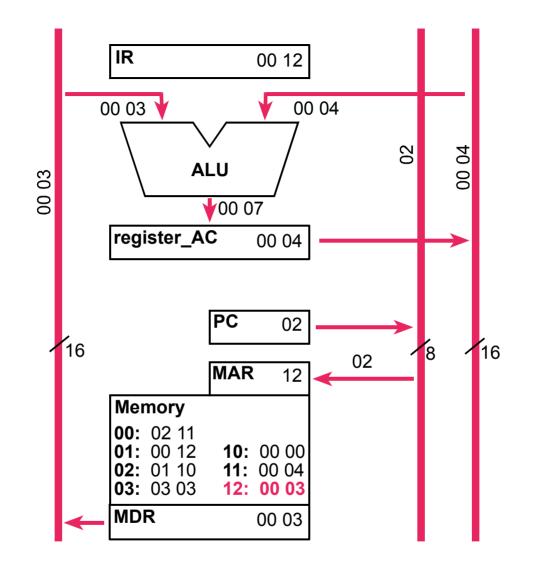

Figure 9.10 Register transfers in the ADD instruction's Execute State.

```

-- Simple Computer Model Scomp.vhd

LIBRARY IEEE:

USE IEEE STD LOGIC 1164 ALL;

USE IEEE.STD LOGIC ARITH.ALL;

USE IEEE.STD LOGIC UNSIGNED.ALL:

LIBRARY altera mf:

USE altera mf.altera mf components.ALL;

ENTITY SCOMP IS

: IN STD LOGIC;

PORT(

clock. reset

: OUT STD LOGIC VECTOR( 7 DOWNTO 0 );

program counter out

: OUT STD LOGIC VECTOR(15 DOWNTO 0):

register AC out

: OUT STD LOGIC_VECTOR(15 DOWNTO 0 ));

memory data register out

memory address register out

: OUT STD LOGIC VECTOR(7 DOWNTO 0);

memory write out

: OUT STD LOGIC):

END SCOMP;

ARCHITECTURE a OF scomp IS

TYPE STATE TYPE IS (reset pc, fetch, decode, execute add, execute load, execute store,

execute store2. execute jump ):

SIGNAL state: STATE TYPE;

SIGNAL instruction register, memory data register

: STD LOGIC VECTOR(15 DOWNTO 0);

SIGNAL register AC

: STD LOGIC VECTOR(15 DOWNTO 0);

: STD LOGIC VECTOR( 7 DOWNTO 0 );

SIGNAL program counter

: STD LOGIC VECTOR( 7 DOWNTO 0 ):

SIGNAL memory address register

SIGNAL memory write

: STD LOGIC;

BEGIN

-- Use Altsyncram function for computer's memory (256 16-bit words)

memory: altsyncram

GENERIC MAP (

operation mode => "SINGLE PORT",

width a => 16,

widthad a => 8,

lpm type => "altsyncram".

outdata reg a => "UNREGISTERED",

-- Reads in mif file for initial program and data values

init file => "program.mif".

intended device family => "Cyclone")

PORT MAP (wren a => memory write, clock0 => clock,

address a =>memory address register, data a => Register AC,

q a => memory data register );

-- Output major signals for simulation

<= program counter;

program counter out

register AC out

<= register AC;

memory data register out

<= memory data register;

memory address register out <= memory address register;

```

**PROCESS** (CLOCK, RESET) **BEGIN** IF reset = '1' THEN state <= reset pc; ELSIF clock'EVENT AND clock = '1' THEN **CASE** state **IS** -- reset the computer, need to clear some registers WHEN reset pc => program counter <= "00000000"; register AC <= "000000000000000"; state <= fetch: -- Fetch instruction from memory and add 1 to PC WHEN fetch => instruction register <= memory data register; program\_counter <= program counter + 1; state <= decode: -- Decode instruction and send out address of any data operands WHEN decode => CASE instruction register(15 DOWNTO 8) IS WHEN "00000000" => state <= execute add; WHEN "00000001" => state <= execute store; WHEN "00000010" => state <= execute load; WHEN "00000011" => state <= execute jump; WHEN OTHERS => state <= fetch: END CASE:

-- Execute the ADD instruction

WHEN execute add => register ac <= register ac + memory data register; state <= fetch; -- Execute the STORE instruction -- (needs two clock cycles for memory write and fetch mem setup) WHEN execute store => -- write register A to memory, enable memory write -- load memory address and data registers for memory write state <= execute store2; --finish memory write operation and load memory registers --for next fetch memory read operation WHEN execute store2 => state <= fetch: -- Execute the LOAD instruction WHEN execute load => register ac <= memory data register; state <= fetch: -- Execute the JUMP instruction WHEN execute jump => program counter <= instruction register(7 **DOWNTO** 0); state <= fetch: WHEN OTHERS => state <= fetch: END CASE: END IF: END PROCESS:

-- memory address register is already inside synchronous memory unit

-- need to load its value based on current state

-- (no second register is used - not inside a process here)

## WITH state SELECT

memory address register <= "00000000" WHEN reset pc, program counter WHEN fetch. instruction\_register(7 DOWNTO 0) WHEN decode. program counter **WHEN** execute add, instruction register(7 DOWNTO 0) **WHEN** execute store, program counter WHEN execute store2, program counter WHEN execute load, instruction register(7 DOWNTO 0) **WHEN** execute jump; WITH state SELECT memory\_write <=</pre> '1' WHEN execute\_store, '0' **WHEN** Others;

END a;

| <b>DEPTH =</b> 256;<br><b>WIDTH =</b> 16; | % Memory depth and width are required %<br>% Enter a decimal number % |   |

|-------------------------------------------|-----------------------------------------------------------------------|---|

| ADDRESS_RADIX = HEX                       |                                                                       |   |

| DATA RADIX = HEX;                         |                                                                       |   |

| ,                                         | % otherwise specified, radixes = HEX %                                |   |

| Specify val                               | ues for addresses, which can be single address or range               |   |

| CONTENT                                   |                                                                       |   |

| BEGIN                                     |                                                                       |   |

| [00FF] : 0000;                            | % RangeEvery address from 00 to FF = 0000 (Default)                   |   |

| 00 : 0210;                                | % LOAD AC with MEM(10) %                                              |   |

| 01 : 0011;                                | % ADD MEM(11) to AC %                                                 |   |

| 02 : 0112;                                | % STORE AC in MEM(12) %                                               |   |

| 03 : 0212;                                | % LOAD AC with MEM(12) check for new value of FFFF %                  |   |

| 04 : 0304;                                | % JUMP to 04 (loop forever) %                                         |   |

| 10 : AAAA                                 | ;% Data Value of B %                                                  |   |

| 11 : 5555;                                | % Data Value of C%                                                    |   |

| 12 : 0000;                                | % Data Value of A - should be FFFF after running program              | % |

| END ;                                     |                                                                       |   |

Figure 9.12 MIF file containg  $\mu P$  Computer Program.

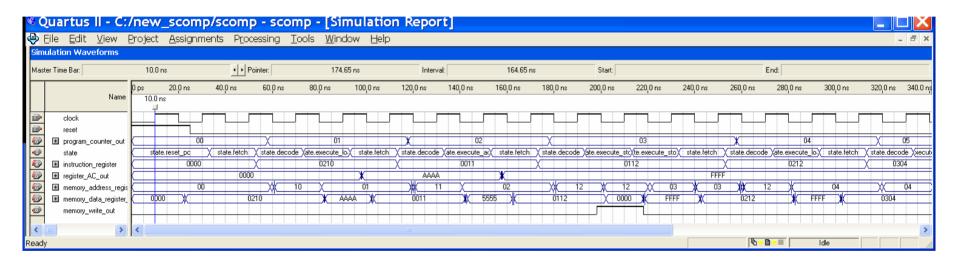

## Figure 9.13 Simulation of the Simple µP Computer Program.

| Second Stress       Second Stress< |                                                                    |      |      |      |      |      |      |      |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|------|------|------|------|----------|

| SCOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCOMP   altsyncram:memory   altsyncram_7af2:auto_generated   ALTSY |      |      |      |      |      |      |      |          |

| Addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +0                                                                 | +1   | +2   | +3   | +4   | +5   | +6   | +7   | ^        |

| 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0210                                                               | 0011 | 0112 | 0212 | 0304 | 0000 | 0000 | 0000 |          |

| 08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | АААА                                                               | 5555 | FFFF | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 |          |

| 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000                                                               | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | <b>*</b> |

**Figure 9.14** Simulation display of µP 3 Computer Memory showing result stored in memory